# IC設計攻頂補助計畫

# 說明簡報

經濟部產業技術司

112年12月

## 報告內容

- 一. 背景說明

- 二. 推動領域及補助範疇

- 三. 申請對象及申請資格

- 四. 補助科目及比例

- 五. 審查重點

- 六. 申請注意事項

- 七. 申請應備文件

- 八. 審查流程

- 九. 預定作業時程

- 十. 其他

# 一、背景說明(1/2)

■112年3月28日臺灣半導體產業協會(TSIA)發布「臺灣IC設計產業 政策白皮書」,指出:

IC設計產業面臨中國快速崛起、國內人才短缺問題嚴重及投入先進技術/產品的業者屈指可數等隱憂,亟待採取積極作為以鞏固當前的競爭優勢與市場地位。

• 我國半導體產業產值全球第二, IC設計全球第二(市佔率21%), 但僅有39%晶片產值使用先進製程製造

# 一、背景說明(2/2)

■113年行政院啟動「晶創臺灣方案」,以晶片結合生成式AI等關鍵技術,推動全產業加速創新突破。

因應半導體產業的技術趨勢,「晶創臺灣方案」透過晶片設計端、元件製造及封測端、應用端等三構面,推動產學研加速發展異質整合,並邁向先進製程技術。

|                  | 把握領先   | 黄金時期・加速邁向               | 先進集         | 提   |  |

|------------------|--------|-------------------------|-------------|-----|--|

| 晶片設計如            | 耑      | 元件製造及封測端                | <b>&gt;</b> | 應用端 |  |

| 掌握關鍵晶片<br>設計軟體技術 |        | 加速矽製程<1nm技術<br>與非矽基晶片製造 |             | 高算力 |  |

| 提升先進晶片<br>設計能力   | N N    |                         |             | 高頻率 |  |

|                  | Anna a | 3D晶片堆疊技術<br>與異質整合封裝     |             | 高功率 |  |

| 加速異質整合<br>設計及介面  |        | <b>4</b> 6 6 6          |             | 高節能 |  |

■經濟部產業技術司重點推動我國IC 設計業者投入「具國際領先地位」 之晶片及系統研發,藉以提升先進 晶片設計能力、並加速異質整合設 計及介面,以推動臺灣成為IC設計 領導國家。

來源:2023年11月2日公布「晶創台灣方案」

## 二、推動領域及補助範疇

驅動臺灣業者投入先進技術應用晶片,至2026年等同或超越國際標竿大廠技術指標之晶片設計開發、試產與Beta Site驗證。

#### ■補助範疇(四擇一):

- 一. 創新技術之先進晶片開發,採用7nm (含)以下製程。

- 二. 先進異質整合封裝技術之創新晶片(如小晶片整合封裝模組、矽光子等其他新興應用晶片開發)。

- 三. 異質整合微機電感測技術之創新晶片開發,採用0.35µm(含)以下之晶圓級製程。

- 四.優先推動人工智慧、高效能運算、車用電子、下世代通訊等四領域,規格如下:

#### 一、人工智慧:

- √伺服器(推論): 算力 > 500 TOPS

- √裝置端: 算力 > 80 TOPS

#### 三、車用電子:

- ✓輔助駕駛:算力 > 80 TOPS(L2+)

- ✓智慧座艙: 算力 > 40 TOPS

#### 二、高效能運算:

✓ 算力 > 500 TOPS

#### 四、下世代通訊

- ✓ 無線傳輸

- B5G/6G >15 Gbps以上; Wifi >20 Gbps以上

- ✓ 有線傳輸 >800 Gbps以上

註: TOPS(Tera Operations Per Second for INT8; 每秒一兆次操作)

### 1-創新技術之先進晶片開發

#### 產業發展現況

- 臺灣IC設計業約300家業者,僅有不到30家投入16nm以下先進製程開發

- 先進製程技術節點成本高昂,矽智財、EDA tool、1x奈米用光罩等研發費用超出新臺幣30億元

- AI、HPC、車用等晶片,對運算能效具高規格需求,採先進製程可直接提升產品競爭力

### 提升技術作法與效益

- 作法:提升國內IC設計業具有7nm(含以下)製程開發能力,並開發比局或超越國際標竿大廠晶片設計技術

- 效益:

- 提升高算力與高節能的晶片設計能力,並在如AI/HPC/車用(自動駕駛、中控晶片)...領域領先國際

- · 可與中國IC設計業往成熟製程發展形成差異化

OEA

### 2-先進異質整合封裝技術之創新晶片開發

#### 產業發展現況

- AI、HPC等晶片朝先進異質整合封裝與小晶片架構發展,目前台廠僅少數業者 投入開發

- 因應運算效能所伴隨的高速資料傳輸需求,未來對先進異質整合封裝技術,如 矽光子共同封裝光學技術(CPO)有強烈需求

### 提升技術作法與效益

- 作法:整合先進異質整合封裝上下游供應鏈技術,並接軌國際小晶片生態系

- 效益:

- 強化高算力與高節能的晶片設計能力,透過異質整合封裝技術提升競爭力

### 3-異質整合微機電感測技術之創新晶片開發

#### 產業發展現況

- 臺灣晶圓級感測器與異質整合封裝等製造業者已逐漸茁壯,但IC設計仍須技術研發資源投入

- 異質整合微機電感測創新晶片可應用在創新應用領域,如:生醫(生物晶片)、 農業(智慧農業)、車用感測(自動駕駛、ADAS)、工業(智慧工廠)…等領域

### 提升技術作法與效益

- 作法:整合晶圓級感測器與異質整合封裝上下游技術,有助於提升晶片競爭力

- 效益:

- · 提升異質整合微機電感測晶片設計能力,並在如生醫、農業、車用感測、工業...等新興領域領先國際

### 4-人工智慧、高效能運算、下世代通訊、車用電子等 優先推動領域

#### 產業發展現況

- 傳統的資通訊用半導體已成長趨緩,需要有新的應用領域來驅動成長

- AI、HPC、下世代通訊、車用電子,為全球IC設計業前十五大業者主要的未來 布局技術項目

#### 提升技術作法與效益

- 作法:標竿國際最領先規格,加速晶片技術創新

- 效益:

- ✓ AI:伺服器(推論):算力 > 500 TOPS、装置端:算力 > 80 TOPS

- ✓ HPC: 算力 > 500 TOPS

- ✓ 車用電子:輔助駕駛:算力 > 80 TOPS(L2+)、智慧座艙:算力 > 40 TOPS

- ✓ 下世代通訊:無線傳輸 B5G/6G >15 Gbps以上; Wifi >20 Gbps以上、有線傳輸 >800 Gbps以上

## 三、申請對象及申請資格

#### ■申請對象

✓本計畫以補助我國IC設計相關業者為主,可由單一企業或多家企業(結合上下游合作廠商,但須由IC 設計業者主導)聯合申請。

#### ■申請資格

- 1. 國內依法登記成立之本國公司,含獨資、合夥、有限合夥事業或公司,本國公司之認定:

- 1) 若本國公司為外國公司依中華民國公司法在臺登記之分公司、或本國公司為外國公司之從屬公司,非屬本計畫認定 之本國公司。

- 2) 若原依中華民國公司法在臺設立登記之本國公司,後因公司營運發展將部份業務轉移至國外或更改股權結構成為外 國公司之從屬公司,但仍於中華民國境內進行主要營運與研發者,視為本計畫認定之本國公司。

- 2. 非屬銀行拒絕往來戶,且公司淨值(股東權益)為正值。

- 3. 不得為陸資來臺投資事業;其依本部投資審議委員會之陸資來臺投資事業名錄認定之。

- 4. IC設計相關業者包括:從事IC設計、IC設計服務、矽智財、EDA、提供異質封裝設計與服務相關業 者,且須<mark>提供服務實績</mark>進行佐證。

## 四、補助科目及比例

- 補助比例最高不超過計畫總經費之50%,其餘部分由申請單位自籌

- 授權與委託比例超過總經費40%以上(含),須敘明理由

# 五、審查重點

| 審查重點<br>(計分比例)    | 內涵說明                                                                                                                                                    |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| (一)技術層級<br>(40%)  | 1.技術領先性:突破與攻堅之先進技術與國際技術領先大廠相比,具有領先性或等同。<br>2.技術自主性:技術項目規劃布局完整性、已有專利分析,且計畫內有明確規劃核心IP佈局。<br>3.技術實現性:技術研發策略明確可行,且研發成果/產品(晶片或系統)需提供相關測試驗證進行佐證,列入計畫查核點。      |

| (二)市場價值<br>(30%)  | <ul><li>1.市場競爭力:目標市場及客戶、預期產出價值及後續擴散效益具有明確性;預期結案後可提升營業指標成長率、具體的投資營運規劃。</li><li>2.技術價值性:產業帶動效果及預估帶動規模大小。</li><li>3.合作共創性:有明確提出帶動國內廠商合作共創之構想及作法。</li></ul> |

| (三)計畫可行性<br>(30%) | <ul><li>1.計畫主持人及計畫團隊配置與執行經驗是否適宜,聯合提案之主導企業是否具計畫整合能力且團隊分工清楚。</li><li>2.計畫經費編列合理性。</li><li>3.查核點及驗收規劃的合理性與可行性。</li></ul>                                   |

| 加分項目<br>(最多10%)   | 基於未來市場成長性、標竿國際大廠投入與前瞻技術布局,對於攻堅 <b>人工智慧、高效能運算、下世代通訊、</b><br>車用晶片等領域提案者,將依攻堅技術難度給予加分鼓勵(最高給予10分)。                                                          |

經濟部產業技術司 Department of Industrial Technology, MOEA

ent of Industrial Technology, MOEA

## 六、申請注意事項

- ■本計畫採批次收件、批次審查,依最終評核結果及推薦順序,擇優對象予以補助。

- ■本計畫申請主導廠商以一案為限,且與「驅動國內IC設計業者先進發展補助計畫」(產業發展署)擇一申請。本計畫(產業技術司)主要補助大廠攻頂,包括先進製程、新興技術等的國際領先,產業發展署則主要補助中小型業者邁入先進晶片、創新應用產品化與落地。

- ■計畫時程:以不超過5年為原則。

- ■申請計畫者,應於公告受理期間研送計畫書,受理日期自公告日起算7日後開始受理至 113年3月29日下午五點止(以郵戳或收件章為憑),由本部籌組審查小組進行審查,核定 通過後簽約執行,計畫執行期程可回溯至113年4月1日。

- ■無形資產/技術引進應註明是否為政府計畫成果,若是,則該無形資產引進應編列於自籌款;委託研究亦應標註是否為政府計畫成果,若是,須註明該政府計畫名稱並說明本申請計畫委託之技術項目與該政府計畫技術之區別。

- ■本計畫優先支持採用國內IP,且研發試產投片(shuttle)對象須為國內晶圓廠,如有特殊需求者,請敘明理由。 DOIT

經濟部產業技術司 Department of Industrial Technology, MOEA

## 七、申請應備文件

1式2份

- 計畫申請表

- 申請公司基本資料表

1式10份

- 計畫簡報

- 計畫書

1式1份

- 主導公司最近3年會計 師簽證查核報告書

- 聯盟公司近 1 年會計師 簽證查核報告書

■ 送件地址:

「經濟部產業技術司A+企業創新專案辦公室」 臺北市中正區100409重慶南路二段51號 永豐餘大樓7樓

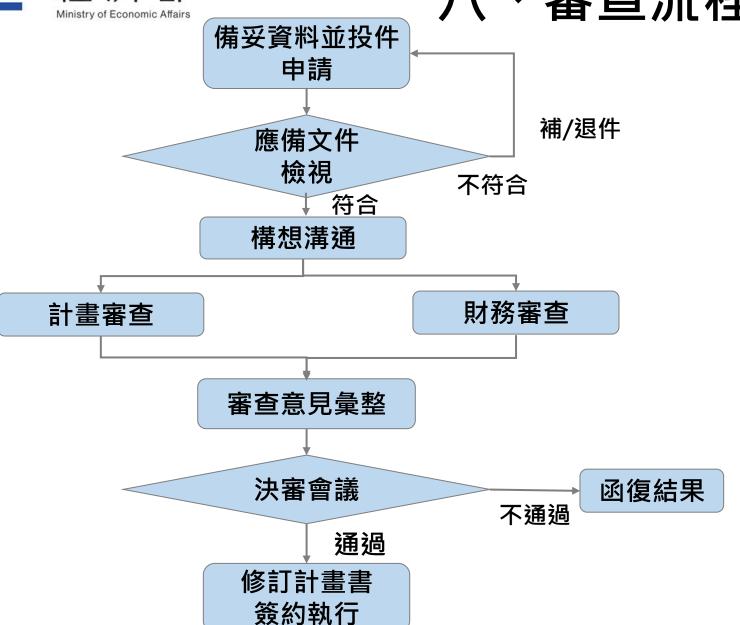

## 八、審查流程

- ✓ 計畫採批次收件、批次審查, 依最終評核結果及推薦順序, 擇優對象予以補助。

- ✓ 申請廠商可於構想溝通後,自 行評估是否調整計畫簡報/計畫 書,如有調整,須至少於計畫 審查會議前一周提供。

- ✓ 決審通過之申請廠商必須依據 決審會議決議事項,在規定時 間內提供修訂版計畫書,經主 審確認後始能進行簽約。

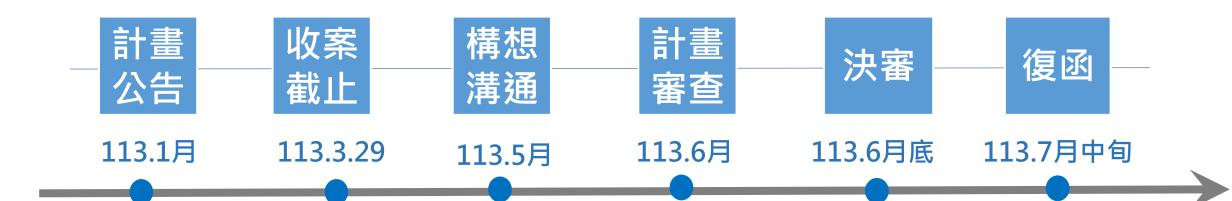

## 九、預定作業時程

## 十、其他

- ■除前列各項公告事項外,其他申請資格、申請應備資料等相關規定, 請詳見計畫申請須知。

- ■申請須知相關資料,可由本部技術司「IC設計攻頂補助計畫」網站 (https://aiip.tdp.org.tw/)下載取得。

- ■送件地點:「經濟部產業技術司A+企業創新專案辦公室」 (臺北市中正區10075重慶南路2段51號永豐餘大樓7樓)。

- ■申請諮詢電話:A+企業創新專案辦公室 林小姐

(電話:02-2341-2314分機2216、傳真:02-2341-2094、02-2392-9477)