:::

科技新知

半導體小晶片(Chiplet)模式暨異質整合封裝發展趨勢

發表日期:2021-01-27

作者:楊啟鑫(工研院)

摘要:

晶片整合技術發展已久,由過去PC時代整合在主機板方式,進而演變成手機與物聯網時代以封裝方式整合,以達縮小體積與降低耗電以符合終端產品需求,而在今日晶片發展至7奈米量產,晶片成本不斷上升,AI與高速運處晶片功能不斷增加導致晶片需求面積愈來愈大,先進封測技術已成為降低晶片成本不可或缺的重要利器。

全文:

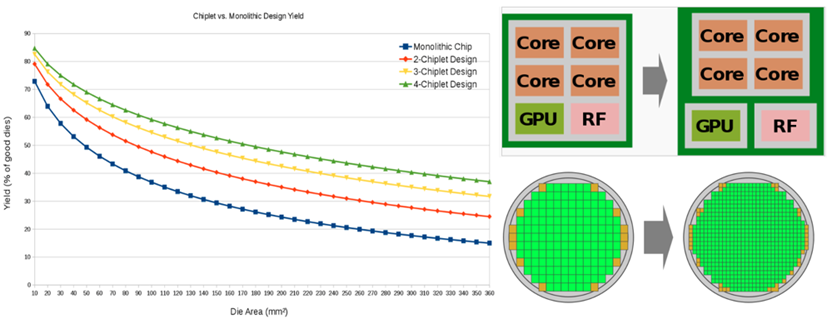

一、昂貴的先進製程晶片成本驅動小晶片整合模式發展

先進產品持續朝向高效能、低功耗及多功能效益發展,當先進製程發展到28奈米之後,愈加昂貴的先進製程晶片及持續提升效能的高速運處晶片需求帶動下,高效能的先進製程晶片扮演高階製程晶片之重要角色,然而另一方面晶片成本亦面臨快速上升的處境,當晶片成本的摩爾定律已經失效情況下,業界發展出一套將大晶片切割成小晶片模式的設計方式以降低晶片製程端的成本(如圖1所示),再以高階封裝如CoWoS(Chip On Wafer On Substrate ; tsmc技術)或EMIB(Embedded Multi-Die Interconnect Bridge ; Intel封裝技術)的方式將晶片整合起來,以維持原先SoC效能的同時,又能達到比原先SoC更低的成本方式來製作先進製程晶片,另一方面,在晶圓廠導入先進封裝的趨勢中,晶圓廠的先進封裝都是優先導入最先進製程中,是因最先進製程良率不穩定而導致的高成本,需以小晶片方式來降低其成本,而當N-1代(如目前製程到5 nm,則N-1代則是7 nm製程)製程因良率逐漸穩定,是故在某些不太大顆的晶片上,反而已不需用小晶片模式加以先進封裝來整合。整體而言,先進封裝導入先進製程晶片呈現增加的趨勢,反應出晶圓廠開發先進封裝技術符合先進製程客戶需求,且超過一半應用於5G/AI的先進製程晶片預期會使用先進製程晶片並導入先進封裝技術,以確保成本及效能可達到平衡狀態。

資料來源:WiKiChip(2020/03)

圖1 小晶片模式可提高晶片良率並降低晶片成本

二、DARPA CHIPS推動小晶片模式發展

當摩爾定律逐漸趨緩,在持續提升產品性能過程中,如果為了整合新功能晶片模組而增大晶片面積,將提高先進製程大晶片成本及遇到製程低良率問題。小晶片(Chiplet)設計模式為業界因應摩爾定律面臨瓶頸所做的技術替代方案之一,其想法源於1970年代誕生的多晶片模組封裝方式,而面臨先進製程愈大愈昂貴的解法就是讓高效能晶片使用最先進製程製造,其它則使用符合經濟效益(亦即非最先進製程)的製程製造(如I/O晶片、記憶體晶片等)。從原來設計在同一個SoC中的晶片,分拆成許多不同的小晶片製造完後再加以封裝達到晶片整合效果,故稱此分別製造的晶片為小晶片chiplet,目前主要用於小晶片整合封裝技術大廠包括tsmc 的CoWoS/SoIC(System-on-Integrated-Chips)、Intel 的EMIB(2D封裝技術)/Fovores(3D封裝技術)、AMD 的MCM(Multi-Chip-Module)晶片整合封裝技術…等。

而隨著半導體產業日益重要,晶片技術亦成為美國國防部計畫之一,美國國防部DARPA計畫旗下的CHIPS分項計畫則是針對晶片如何成為小晶片,再定義IP介面標準及快速晶片模組升級擴充機制,讓晶片達到高效能、低成本及快速完成晶片組裝以供國防設備等使用,而因目前的先進晶片整合封裝大廠在介面上規格不一,同時亦需制定重覆使用IP方式,以減少晶片設計時程,故需將小晶片模組化與規格化,以達到終端使用者僅需將已製作好的晶片模組作組合與擴充便能直接利用,才能減少晶片設計與製造時程(約半年至一年),同時能提高供應鏈的靈活度,且不會因區域戰爭而造成晶片模組缺貨的窘境。

三、ODSA-End User及業界共同制定開放性介面

開放領域特定架構ODSA(Open Domain-Specific Architecture,ODSA)組織,主要是在Facebook創建的開放運算計畫(Open Compute Project,OCP)框架計畫下,其成員包括NXP、FPGA相關IP公司Achronix、安森美半導體(On Semiconductor);新創公司Kandou、SiFive和zGlue等五十多家公司的組織。ODSA的發起人之一Bapi Vinnakota,同時也是網路處理器設計業者Netronome工程師表示:「目前所有的多晶片介面都是專有的,我們這個組織想建立一個開放性介面,讓你可以組裝出最好的晶片。」現階段OSDA的成員主要聚焦於資料中心,但該組織未來目標也包括行動裝置與邊緣系統晶片。而恩智浦半導體(NXP)則認為,將為不同的產業別提出價值主張,並為已知合格晶片(KGD)定義測試認證,同時ODSA還需要吸引包括封裝業者在內的幾個關鍵參與者,共同實現小晶片標準化的模式。

四、結論

晶片整合技術發展已久,由過去PC時代整合在主機板方式,進而演變成手機與物聯網時代以封裝方式整合,以達縮小體積與降低耗電以符合終端產品需求,而在今日晶片發展至7奈米量產,晶片成本不斷上升,AI與高速運處晶片功能不斷增加導致晶片需求面積愈來愈大,先進封測技術已成為降低晶片成本不可或缺的重要利器,換言之,過去可獨立運作的晶片製造與封裝測試,已漸漸整合在一起,這就是為何目前最先進的封測技術,主要開發者是具先進製程技術的晶圓廠或IDM(Integrated device manufacturer),如台積公司與Intel等都開發自家2D到3D封測技術,而且此技術主要導入最先進的製程中,預期未來在AI與高速運算持續需求高效能晶片趨勢下,晶片製程與先進封測技術將逐漸整合,成為虛擬整合晶片,晶圓廠/IDM亦將依產品需求而開發更多先進製程所需之先進封測技術,晶圓廠/IDM將成為先進封測技術開發領導者,而封測廠將逐漸扮演追隨者的角色,協同晶圓廠/IDM佈局晶片製造產業鏈。

(本文作者為工研院產科國際所執行產業技術基磐研究與知識服務計畫產業分析師)

點閱數

點閱數:

1706