:::

科研案例

晶圓級可圖形化光濾波薄膜製程技術研發

發佈日期:2014-01-13

案例摘要:

本計畫創新重點為在原有大面積平板玻璃上製備IR-cut濾波等多層光學鍍膜設計及鍍膜技術,結合微影蝕刻技術,於已有圖形的不平整IC晶圓表面,直接進行光學鍍膜,使IC具備多重感光功能,增加IC之價值。因目前國內外尚無類似之技術或產品,故此創新技術具高度之國際競爭力。

藉由此技術與合作廠商開發出環境光感測、近接感測及手勢辨識等相關應用。並透過計畫的執行,增加乾式電漿蝕刻機之採購,且已進行中華民國之專利申請。

計畫執行完成後,已有IC客戶導入此製程,開發出ALS及PS之IC供貨給韓國二線手機廠使用。民國102年第三季可達1,000片/月,後續預計每年可增加新臺幣2億元以上之營業額。

內容說明:

智慧型手機及平板電腦熱潮歷久不衰,各種炫目功能齊發,其中,在環境背景光源、LED色彩、人員距離、UV紫外線偵測等應用方面,光學感應元件(CMOS Imager)無疑扮演最為關鍵的角色。近年來,光學感應元件技術也迭有進展,然而無論是何種封裝方式都僅能實施單一感光濾光模式,無法滿足未來同一顆IC中具有多重感光區域的要求。耀穎光電的「晶圓級可圖形化光濾波薄膜製程技術」突破了此瓶頸,可在同一晶片上實施多重光學鍍膜,以提供多重光學濾波功能,滿足單一晶片具有多個感光區的應用需求。

基本上,現有光學感應元件結構包括CMOS Sensor、濾光片和透鏡等。傳統的封裝方法是採用晶片直接封裝(COB, Chip on Board)方法,這是一種類似微型的鏡頭結構,將CMOSSensor、濾光片和透鏡以堆疊的方式封裝在一密閉機構內。而為了進一步縮小元件的體積和降低成本,現在還發展出晶圓級(CSP, Chip Scale Packaging)製程技術,這是將八吋的濾光片與八吋的CMOS Sensor晶圓貼合後(wafer level package),再進行切割和封裝。

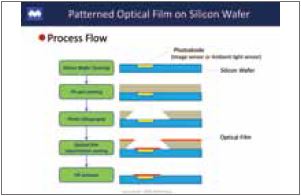

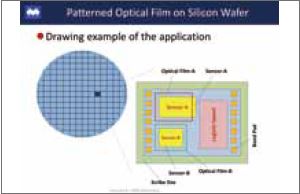

上述兩種方法目前都無法在同一晶片上提供多重感光區域。耀穎光電苦思解決之道,所開發出的晶圓級光學鍍膜製程技術,適足以解決此問題。此技術是將光學薄膜直接實施在晶圓上,並結合黃光製程和光阻劑的應用,可以將不同光譜的鍍膜實施在特定的圖形區域,並藉由重複製程,產生多重的光學鍍膜功能,讓同一IC元件具備多重光感應功能,以提供多重光學濾波功能,使單一晶片可具有多個感光區。

此技術的研發不易,在於現有的光學鍍膜技術都是在平坦的玻璃上實施,而此技術是要在晶圓(如8吋晶圓)表面上直接實施光學鍍膜技術,如此就必須克服晶圓表面不平整的困難,不僅要實施鍍膜且需達到所要求的光學特性。綜觀目前國內外尚無類似產品及技術,耀穎光電的突破可謂領先產業。

此技術的開發成功,讓耀穎光電的整體技術能量大為提升,且衍生出ALS(環境光感測)、PS(近接感測)、Gesture(手勢辨識)等相關應用,耀穎光電並持續投資相關機台設備,例如乾式電漿蝕刻機等。該公司預估未來將達到每月1,000片以上的產量需求,年銷售金額在新台幣2億元以上。在市場實績方面,目前已有國內IC設計客戶利用此技術完成雙重光感應IC的開發,並獲韓國二線手機品牌廠評估採用,預估採用此技術的客戶因業務擴展,年營業額約可增加新台幣10億元以上(每顆晶片以0.4美元計算)。

就產業創新的角度來看,此計畫所專注的「晶圓級可圖形化光濾波薄膜製程技術」,提出了一個全球產業尚未有先例的解決方案,讓IC得以具備多重感光功能,IC價值倍增,此創新技術無疑具高度國際競爭力,且能為台灣半導體業界注入創新活力。

Method of Patterning Optical Film on Silicon Wafer_MOE_20130423-5

Method of Patterning Optical Film on Silicon Wafer_MOE_20130423-6

點閱數

點閱數:

3480