:::

科技專案成果

創新前瞻技術研究計畫-先進半導體製程量測技術

發佈日期:2012-07-11

單位:工業技術研究院

案例年度:2010

簡介:

工業技術研究院量測技術發展中心顧逸霞博士自2004年起主持先進半導體製程量測技術開發計畫,為國內前瞻科專研究首度跨入先進半導體製程最關鍵、技術難度最高且長期為國外前幾大品牌設備廠商瓜分之微影製程領域。計畫執行期間顧博士著重於原創技術之研發與專利佈局,充分掌握國際半導體技術藍圖(ITRS)未來發展時程與技術需求,開發次世代65/45/32奈米半導體製程In-line即時量測技術,領先國際半導體技術藍圖之製程檢測需求時程3年以上,同時與多家國際半導體製造大廠合作於先進量產製程上驗證量測效能,對提升先進量產製程產品良率以及縮短產品上市時間有著深遠貢獻。

特色:

顧逸霞博士發展前瞻奈米製程所需之檢測技術,成果卓越。

- 於先進半導體製程之奈米級檢測技術有諸多突破,尤其在In-Chip疊對量測、製程線寬量測技術的貢獻,相當傑出。

- 技轉成果豐碩,七年內有超過新台幣8,000萬元之技轉成就,凸顯其研究對全球半導體奈米製程檢測的產業效益。

- 顧博士以物理光電等理論為基礎,帶領團隊發展出前瞻量測技術與分析演算法,對我國高科技(半導體)製程檢測及良率提升有關鍵性貢獻,確為我科技女傑獎之表率。

- 新創雷射散射儀之檢測技術及亮場顯微影像檢測技術,學術理論及產業應用皆有傑出表現。

- 著作及專利產出豐碩,連續七年獲工研院SCI論文獎。

計畫成果:

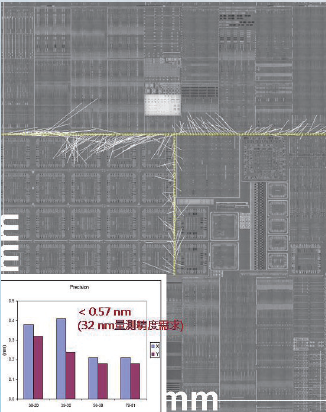

1. 開發亮場顯微影像檢測技術應用於先進微影製程疊對誤差(overlay) In-line即時檢測,量測精確度可達0.57奈米以下。

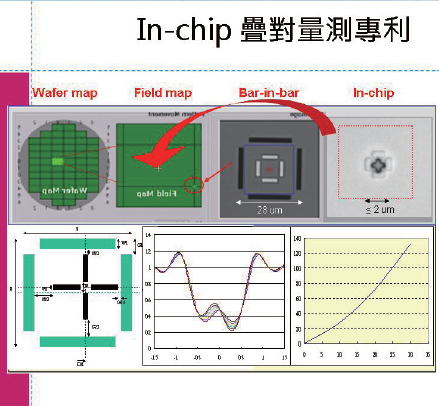

2. 研發世界領先之原創性In-chip微影製程疊對量測專利設計,發展奈米結構繞射成像理論以達最佳化製程量測設計。

3. 開發雷射散射儀檢測技術應用於關鍵尺寸(Critical dimension)、線寬粗糙度(Line width roughness)、側壁角度Sidewall angle)、疊對誤差等多參數In- line即時檢測回饋控制,關鍵尺寸量測精確度可達0.58奈米以下。

4. 建立32奈米先進半導體製程量測技術平台,使用電磁理論建立3D奈米結構量測理論模型,評估並驗證最佳化量測設計。

5. 將研發能量延伸應用至新興半導體製造3D IC製程檢測,建立突破性的紅外共焦顯微檢測技術,在不破壞高密度堆疊之待測晶片的情況下,達到高解

析度之疊層對位及疊層結構三維形貌量測分析。

6. 申請國內外55件專利,SCI論文9篇、其他國內外期刊與研討會論文47篇。

In-chip 疊對量測專利

In-chip 疊對量測製程驗證

點閱數

點閱數:

2231